So, this week I thought about Thomson EFCIS graphic controllers again. I

know that Thomson made at least two families of controllers, the EF934x, which

runs the Minitel, and the EF936x, which is designed for pixel graphics, but I

did not know as much about this one. It seems a bit more of a "high end" thing,

but at the same time, it is loosely similar to the display system used in

Thomson TO and MO microcomputers.

I also knew that Thomson EFCIS sold the color palette circuit originally

developped for the TO9 as a general color palette chip (the TO9 has it described

as a custom chip in its technical manual, but then it became an off the shelf

chip).

Anyway, I became curious about the other chips and why and how they were

designed. And then I read a lot of datasheets and research papers and patents.

Here is what I found.

Note: this is based on some random web searches, I wasn't there at the time

(in fact I wasn't born at the time) and I could be misunderstanding or misremembering

what I read. Don't trust me too much...

What are we talking about, anyways?

EFCIS is a French semiconductor company. It was created by a public research

lab which turned part of its activity into, apparenly, an integrated circuit

design and manufacturing company. At the time, France was a bit behind the USA

in terms of semiconductors manufacturing. The government helped solve this by

injecting money into the sector, but also there would be various merge of companies

to join forces, and partnerships with US companies to first resell their chips,

and then manufacture them locally.

In the case of EFCIS, it would merge with several other companies to become

Thomson Semiconducteurs, which in turn merged with Italian SGS to become

SGS-Thomson, later shortened to ST Microelectronics. That company is still

around today.

But our story does not start there. Instead, we have to dig into what was

happening in the mid-70s in the Laboratoire d'Informatique de l'École Normale

Supérieure (LIENS). That's another French reserach lab that, at the time,

worked on computer systems and architecture. This is the 70s, so we're talking

about probably only one computer, and various terminals to serve it. The

terminals would either be text-only, or graphic ones such as the Tektronix 4010

series.

These terminals are somewhat complex and costly hardware. The 4010 is a strange

device by today's standard, it does not use RAM to store display data, instead,

the cathode ray tube itself keeps the pixels "on". This makes the system cheaper,

but has the major downside that you can only erase the whole screen, not just

subsets of it, and erasing takes a second or so. As a result, this is not giving

a great user experience for interactive graphics.

So, the people at LIENS have an idea: what if we could use a TV and some RAM

to make a cheaper terminal? It would allow interactivity, and also maybe color.

Their first try was a text terminal. This was reasonable to do, with 1Kx8bit

of RAM and a character ROM, it is possible to display a 64x16 character grid on

a TV. This allowed to have a first go at generating the display timings, clock,

and pixel shifting.

There was already prior art in doing this, for example, Dan Lancaster's

TV Typewriter from 1973 is

based on very similar concepts (at only half the resolution, 32x16 characters).

That TV typewriter allowed home computers to get some kind of cheap terminal system,

and the video output in early home computers like the Apple I and the SOL-20 were based

on this design.

Anyway, with the goal of making the cost lower, one solution is to reduce

the number of chips by using an LSI (large scale integration) chip. This would

result in the SFF96364, with a patent application in early 1977 (FR 77.0524, also known as FR2382049B1, and its equivalent US patent US4328557A, attributed to Jean Gastinel), I think just

a little time before similar chips like the MC6845 were announced (but it's

hard to find exact dates).

Of course, there would be no point in manufacturing an LSI chip just for use

in the research lab, and so, the SESCOSEM, the chip manufacturer, also introduces

it for sale to the general public. I have not introduced the SESCOSEM yet, but

I don't have much info on it, it seems it merges with EFCIS just a few months

after releasing this chip, and the chip is then rebranded as EF9364.

It's also

worth mentionning that SESCOSEM was also a second source for Motorola products.

Well, or at least that's how they advertised it, it looks like initially, the

chips were manufactured by Motorola but rebadged with SESCOSEM part numbers.

This means you could get both the 6845 and the 96364 from the same company.

However, the two chips, while similar in the way they drive the CRT, are

different on the way they are interfaced on the other side. The 6845 is designed

for use with a microprocessor (initially a 6800, but people figured out how to

make it work with other CPU families as well). On the other hand, the 96364 is

designed instead to interface directly with an UART chip. This means the chip

is less flexible and has a fixed resolution of 64x16 characters, whereas the

6845 can be configured into many videomodes, but on the other hand, and unlike

the 6845, it will manage memory writes and cursor movement, with some special

commands allowing to move the cursor around.

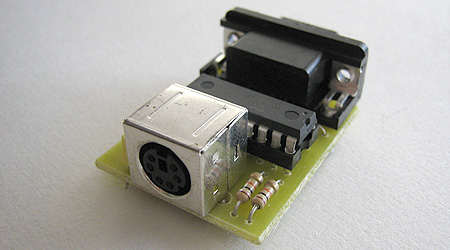

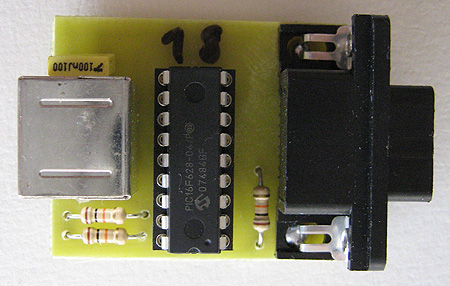

This makes it possible to build a serial terminal ("glass teletype") from a TV

set, this chip, an UART, a character generator and 1Kx7 of RAM, with a bit of

glue logic.

So, we now have this chip that makes it easy and reasonable for DIY computer

builders to assemble a text terminal for their computers. This is taken up

by several electronics magazines and kit distributors, one of the well-known ones

being the Elektor Elekterminal. Suddenly it is possible to build a terminal that

will not require hundreds of TTL chips, or include a microcontroller, and cost

more than the computer it is attached to.

Into graphics controllers

But for the LIENS, this was just a first test of the concept. Their plan is

not to do just text, they are working on designing hardware, and they want to

use CAD applications. They want to replace the Tektronix 4010 with a TV set and

a relatively cheap adapter board.

As the SFF96394 is finally made available to the general public in mid-78,

with terminals and VDU cards starting to appear as kits or prebuilt at the end

of that year, the design for the next system is published, as four patents and

a paper in SIGGRAPH 78 from Philippe Matherat.

Now my research was made quite a bit easier because he links to all of this from

his personal website :).

So, this next design retains the basic idea of designing a chip for use in a

Terminal. However, at this time, and for a more complex graphics terminal, it

becomes acceptable to include a microcontroller, or maybe even a microprocessor

and turn the terminal into a kind of simple workstation. This design aims to

once again reuse a standard TV receiver as the display, but support Tektronix's

PLOT10 API or even Tektronix serial line protocol. This way, the existing

applications will run on the new, cheap terminal as a starting point, and then

the terminal can be extended with color display, faster refresh times, etc.

At the time, the main constraint is not so much on the memory size. 16K DRAMs

are now available at an acceptable price for this application. The main problem

is rather the memory speed. It is not possible to output single bits from a single

DRAM chip fast enough to match the needed pixel clock (the project aims for a

512x512 interlaced display window). The soluion to this is to put several DRAM

chips in parallel (as you do when building a computer to address them in bytes),

and then use a shift register to send the bits to the display circuit.

Essentially, this removes the character ROM from the previous text based system,

instead feeding the RAM output directly into the already existing shift register.

This way, the shift register is the only thing that needs to be really fast,

the RAM will only need to fetch one 8-bit word at a time.

The second problem is fast vector drawing. Microprocessors at the time could

not be programmed to do this fast enough to keep up with even the Tektronix

terminals. Part of the reason for this is that the RAM is completely busy with

sending pixels to the display in this design, probably to keep it simpler. Other

machines at the time (such as the Apple ][) are figuring out how to intermix

accesses to the RAM for the display and CPU, but here a different direction is

taken. The CPU will have only limited access (in fact, it's possible to have

no access at all) and instead the hardware will provide high level drawing

commands, with the goal of drawing one pixel per clock cycle (during borders and

blanking, when the memory is not busy with either display or refresh cycles).

The commands start with vector operations. The display controller keeps track

of X and Y pointers and implements Bresenham's algorithm in hardware for drawing

straight lines. Additionally, it can also draw characters (from the ASCII) table,

with optional scaling, rotation, and slanting.

The chip internally manages a 4096x4096 coordinate space, of which a part is

not visible on screen. This allows line vectors to go out of screen and the drawing

to continue correctly with the next vectors. The part that would be outside the screen

are clipped cleanly and the drawing is not distorted.

Access to the memory is done in parallel (all 8 chips) when reading, but writes

are done one bit at a time, by enabling the RAS pin for just one of the chips.

The SFF96364 could fit in a 28 pins DIP package, but the new EF9365 needs a 40

pins package, and even that is a bit too limiting, so a few extra chips are needed:

a demultiplexer to select the RAM chips, a shift register, and also a PROM to derive

some signals from the clock. The EF9366 is a simplified version that can only draw

a 256x256 display, but requires a little less support logic. Both versions of the

chip do include a lightpen controller as well.

Color graphics are possible by adding parallel banks of memory chips, typically

one for each of red, green, and blue. Then, the CPU can program an external register

to store a 3 bit color, that is loaded to the RAMs when a pixel needs to be plotted.

In one of his later articles, Philippe Matherat explains why this approach

turned out not to be such a great idea: it was done with the goal of replacing

the Tektronix displays, and it did a decent job at that. But, a few year laters,

bitmap displays would become more common, and faster CPUs such as the 68000 would

be available, which would do a faster job at drawing lines and text than this

chip could do, and also allowed more advanced operations (scrolling, overlapping

windows, etc).

There were attempts to workaround these limitations, for example by adding

extra operators on the data path between the video controller and the RAM for

write operations. That would allow some operations like XOR with a cursor,

intersection with existing drawings, etc. However, adding more complex drawing

primitives require a larger redesign of the chip, more on that later.

Initially the chip finds some use, both in DIY videocard projects (again with

Elektor offering one) and in scientific hardware where it makes it possible to

show realtime and color display of measurements (for example I read about its

use to display spectrograms). While the initial design was ready by may of 1978

(as you can see in the patents and papers published then), the chip would be

available to customers only in late 1979 or early 1980. At that time, computers

and workstations with raster graphics are quickly catching up, which means the

chip did not really get a chance to be used.

Meanwhile, in Brittany, ...

Meanwhile, other innovations are going on in France. There are experiments to

replace the phonebook with an electronic device, basically a terminal that would

be plugged into a phone line and allow to send and receive data. Experiments

on this start at about the same time in 1978. Of course, the plan is to replace

the phonebook, which means the terminals will have to be produced in a large

quantity, and be cheap. This justifies the use of an LSI chip again.

This time, there is no room for complex graphics: in a desire to keep the costs

low, there are big constraints on the amount of RAM and ROM in the terminal.

And so, it's back to the simple character based system. But maybe not quite so simple

as the EF9364. The people working on this first experiment with hardware and

protocols based on ANTIOPE, the early Teletext system in France. They also want

to make the terminal user friendly, and for this they need various character

attributes, maybe colors (eventually it will be 8 greyscale levels), double

size characters. Hardware vertical scrolling ("roll") also seems useful to render

long pages of text at an acceptable speed.

These requirements will lead to a new design, initially as a set of two

chips based on the earlier combination of a text mode controller with a character

generator. Eventually, both of the chips become a lot more complex than what they

were initially, and, as it seems usual for EFCIS, they are not reserved to the

Minitel and added to the general catalog of available ICs. These are the EF9340 and EF9341,

also known as VIN and GEN and introduced in 1980. They will also find an use in the Philips Videopac+ consoles

where their video incrustation support will be used to mix the video signal with the

existing one from the Intel 8244 in the older generation Videopac.

The Minitel hardare will be revised several times over the years, to introduce

new features (such as a dialer and local phonebook, and a generic ASCII 80 column

terminal mode). This leads to new generations of video controllers, the EF9345

(introduced 1983, also ends up being used in the Matra Alice computers as well as the

Philips VG5000) and the TS9347 (introduced 1988, with EFCIS now renamed Thomson Semiconducteurs,

this one gets a new manufacturer prefix).

These chip are quite far from the initial "dumb terminal" usage. They can

redefine some custom characters in RAM, have a "compression" system where a

short byte sequence can expand into a longer string that is stored in memory,

etc. They also provide a rather large 8x10 font, fitting 40x25 characters in

a 320x256 video output.

Ok, back to the pixel based ones

The EF936x family also gets an upgrade in the form of the EF9367. This chip

allows doubling the horizontal resolution (to 1024x512 pixels), but it does

so in a not so convenient way. It looks like this was first done as an extension

to an EF9365 videocard, and then pushed back into the video chip. It also changes

the video timing: the initial timing for the 9365/66 resulted in a square, 256x256

or 512x512 window at the center of the display. But, this results in a lot of

wasted space to the left and right of that window. The new chip changes the

timing, it now operates on a slower clock but keeps the same horizontal frequency

for the display. As a result, in 256x256 or 512x512 interlaced modes, the pixels

will be slightly wider than high, matching the 4:3 ratio of the display,

and at 512x256 or 1024x512 interlaced modes, they will be slightly higher than

wide, with a ratio around 2:3, still much better than the 1:2 you would get in

the same conditions with the original chip.

Another new feature is the possibility of a 60Hz mode, reducing the video

resolution. The datasheet and appnotes also add a few extra tricks to the

circuitry, showing how to implement vertical scrolling (useful on the 60Hz version

because it reduces the vertical resolution, and so, parts of the pixels stored in

RAM are actually not visible).

Finally, one last iteration is the TS68483. This is a much extended design,

made to interface with a 68000 CPU and its 16 bit databus (but 8 bit access is

also still possible). It adds more complex drawing primitives for curves,

arcs, and so on. It also uses a larger 64 pin DIP package, which allows to have

more of the logic integrated in the chip, for example, external shift registers

are not needed. It can also produce even higher video resolutions. But, at this

point, the design with memory completely isolated from the CPU is not appropriate

anymore. Graphics terminals are a thing of the past, and other computer systems

have shown that it is possible to get quite fast drawing in software, or, if

there is anything to accelerate, it's rather moving blocks of data around, with

something like a blitter.

Anyway, the EF936x series remains an ahead of its time graphics accelerator.

It would take a few more years to see 2D acceleration implemented in hardware,

and 3D acceleration would follow.

But what if 8 colors is not enough?

In the EF936x documentation, it is suggested to use 3 bitplanes for an RGB

image. This is similar to what was used in the Thomson TO7, but it felt quite

limiting. Later models at Thomson Microcomputers added a 4th bit of color,

either darkening or brightening the other colors. This was implemented by feeding

the 4 color bits from the video generator into a lookup ROM, and then a resistor

network. Of course, this can be added to an EF936x system.

But Thomson computers did not stop there. The next step, introduced first in the

Thomson TO9, was to use a dedicated palette chip. This would have 16 color registers that would store a 12 bit color (4 bit each for R, G, and B)

and replace the ROM used in the previous models. Then, the color palette becomes fully programmable. Typically, you can switch to 16 grey levels,

or mix 8 basic colors and 8 greyscales.

Once again, EFCIS is the company manufacturing that chip, first as a custom

chip for the TO9, but later on added to their general catalog as the EF9369.

There is also a later revision, the TS9370, which can handle higher pixel clocks,

and removes the need for a separate video buffer/amplifier, further simplifying

the design. I don't know if there ever was any graphics hardware combining the

color palette chip with the graphics processors (or even the textmode one). These

products were manufactured by the same company, but for different projects, and

it's unclear if the fact that they would fit together quite well is intentional,

or just an happy incident.